# Intel<sup>®</sup> 31244 PCI-X to Serial ATA Controller

**Design Guide**

April 2004

Order Number: 273651-003

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTELR PRODUCTS. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 31244 PCI-X to Serial ATA Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This Design Guide as well as the software described in it is furnished under license and may only be used or copied in accordance with the terms of the license. The information in this manual is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel Centrino, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel Xeoal, IPLink, Itanium, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside, The Journey Inside, TokenExpress, VoiceBrick, VTune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2004, Intel Corporation

| 1 | About      | t This Document                                                                                                                 | 9  |  |  |

|---|------------|---------------------------------------------------------------------------------------------------------------------------------|----|--|--|

|   | 1.1<br>1.2 | Reference Documentation<br>Terminology and Definitions                                                                          |    |  |  |

| 2 | Overv      | view                                                                                                                            | 13 |  |  |

|   | 2.1<br>2.2 | Features                                                                                                                        |    |  |  |

| 3 | Intel®     | <sup>9</sup> 31244 PCI-X to Serial ATA Controller Package                                                                       | 17 |  |  |

|   | 3.1<br>3.2 | Signal Pin Descriptions         3.1.1       VA0, VA1 (V <sub>CCPLL</sub> ) Pin Requirements         Package/Marking Information | 21 |  |  |

|   | 3.2<br>3.3 | Ball Map By Function                                                                                                            |    |  |  |

| 4 | Routir     | ng Guidelines                                                                                                                   | 25 |  |  |

|   | 4.1        | General Routing Guidelines                                                                                                      |    |  |  |

|   | 4.2        | Crosstalk                                                                                                                       |    |  |  |

|   | 4.3<br>4.4 | EMI Considerations<br>Power Distribution and Decoupling                                                                         |    |  |  |

|   | 7.7        | 4.4.1 Decoupling                                                                                                                |    |  |  |

|   |            | 4.4.1.1 Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Decoupling                                                      |    |  |  |

|   | 4.5        | Trace Impedance                                                                                                                 |    |  |  |

|   |            | 4.5.1 Differential Impedance                                                                                                    |    |  |  |

| 5 | Intel®     | <sup>3</sup> 31244 PCI-X to Serial ATA Controller Interface Ports                                                               |    |  |  |

|   | 5.1        | Serial ROM Interface                                                                                                            |    |  |  |

|   | 5.2<br>5.3 | JTAG Interface PCI-X Interface                                                                                                  |    |  |  |

|   | 5.3<br>5.4 | Serial ATA Interface                                                                                                            |    |  |  |

|   | 0.4        | 5.4.1 Direct Port Access (DPA)                                                                                                  |    |  |  |

|   |            | 5.4.2 Extended Voltage Mode                                                                                                     |    |  |  |

|   |            | 5.4.3 LED Interface                                                                                                             |    |  |  |

|   |            | 5.4.4 Reference Clock Generation                                                                                                |    |  |  |

| 6 | Printe     | ed Circuit Board (PCB) Methodology                                                                                              | 37 |  |  |

|   | 6.1        | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller                                                                         | 20 |  |  |

|   |            | Normal Mode (standard SATA driver)<br>6.1.1 Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller HBA Stackup                 |    |  |  |

|   | 6.2        | Extended Voltage Mode                                                                                                           |    |  |  |

|   |            | 6.2.1 Backplane Topologies                                                                                                      | 40 |  |  |

|   |            | 6.2.2 Motherboard Stackup for Backplane Designs                                                                                 |    |  |  |

|   |            | 6.2.3 Backplane Stripline Stackup                                                                                               |    |  |  |

|   |            | 6.2.4 Cable Interconnect With Backplane                                                                                         |    |  |  |

| 7 | PCI-X      | < Layout Guidelines                                                                                                             |    |  |  |

|   | 7.1        | PCI Voltage Levels                                                                                                              |    |  |  |

|   | 7.2        | PCI/X Clocking Modes                                                                                                            | 48 |  |  |

|    | 7.3    | PCI G               | eneral Layout Guidelines                                                              |    |

|----|--------|---------------------|---------------------------------------------------------------------------------------|----|

|    | 7.4    | PCI-X               | Layout Guidelines For Slot Configurations                                             | 50 |

|    |        | 7.4.1               | Protection Circuitry for Add-in Cards                                                 |    |

|    |        | 7.4.2               | PCI Clock Layout Guidelines                                                           | 51 |

|    |        | 7.4.3               | Connecting Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller                    |    |

|    |        |                     | to Single-Slot                                                                        | 52 |

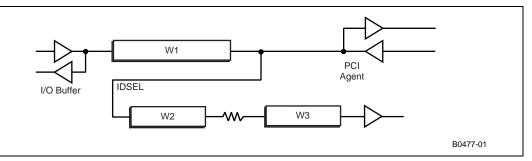

|    |        | 7.4.4               | Embedded Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller<br>Single PCI-X Load | 52 |

|    |        | 7.4.5               | Embedded Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller                      |    |

|    |        | 7.4.5               | Design With Multiple PCI-X Loads                                                      |    |

| 8  | Cable  | and (               | Connectors                                                                            |    |

| 0  |        |                     |                                                                                       |    |

|    | 8.1    |                     |                                                                                       |    |

|    |        | 8.1.1               | Serial ATA Cable                                                                      |    |

| 9  | Volta  | ge Pow              | er Delivery                                                                           | 59 |

|    | 9.1    | Intel <sup>®</sup>  | 31244 PCI-X to Serial ATA Controller Core                                             |    |

|    |        | Supply              | y Voltage: Providing 2.5 V in 3.3 V System                                            | 59 |

| 10 | Test   | Methodo             | ology                                                                                 | 61 |

|    | 10.1   | Exten               | ded Voltage Mode                                                                      | 63 |

|    |        |                     | Extended Voltage Mode Receiver Model                                                  |    |

|    |        | 10.1.2              | 2 Extended Voltage Mode Driver Model                                                  | 64 |

| 11 | Term   | inations            | : Pull-down/Pull-ups                                                                  | 65 |

| 12 | Intel® | )<br>IQ3124         | 44 PCI-X to Serial ATA Controller Evaluation Platform Board                           |    |

|    |        |                     | res                                                                                   |    |

| 13 |        |                     |                                                                                       |    |

| 13 |        |                     | ectors and Logic Analyzer Connectivity                                                |    |

|    |        |                     | ng PCI-X Signals                                                                      |    |

| 14 | Desig  | gn for M            | anufacturing                                                                          | 75 |

| 15 | Therr  | mal Solu            | utions                                                                                | 77 |

|    | 15.1   | Therm               | nal Recommendations                                                                   | 77 |

| 16 | Refe   | ences               |                                                                                       | 79 |

|    | 16.1   | Relate              | ed Documents                                                                          | 79 |

|    | 16.2   |                     | onic Information                                                                      |    |

| А  | Intel® | <sup>)</sup> IQ3124 | 44 Controller Evaluation Platform Board Bill of Materials                             | 81 |

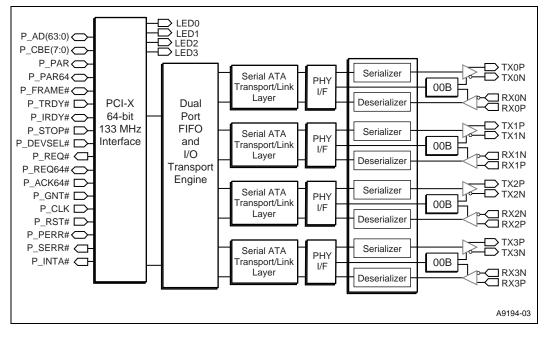

| 1  | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Block Diagram                   | 14 |

|----|-----------------------------------------------------------------------------------------|----|

| 2  | Quad Serial ATA Host Bus Adapter                                                        | 15 |

| 3  | Packaging Considerations                                                                |    |

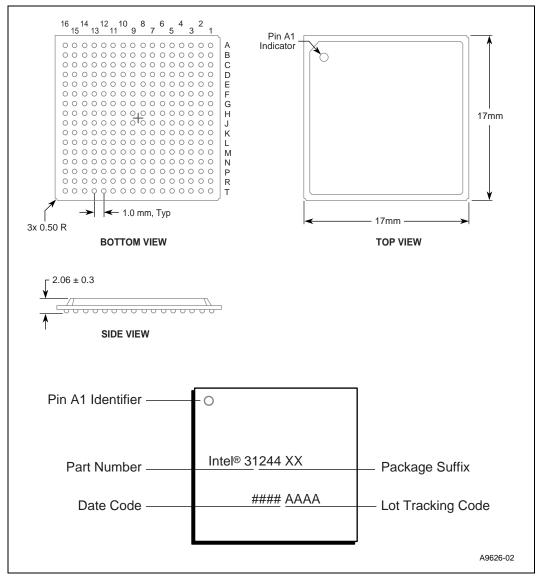

| 4  | Package Information: 256-pin PBGA                                                       | 22 |

| 5  | PBGA Mapped By Pin Function                                                             |    |

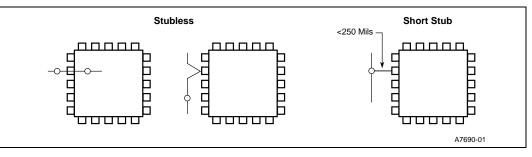

| 6  | Examples of Stubless and Short Stub Traces                                              | 25 |

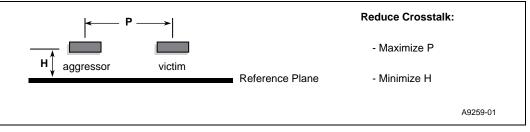

| 7  | Crosstalk Effects on Trace Distance and Height                                          | 26 |

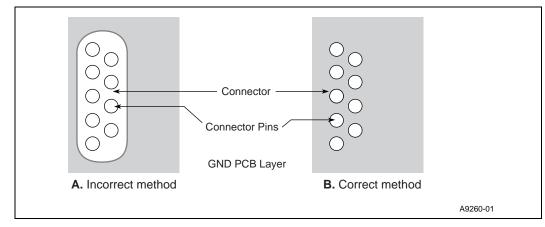

| 8  | PCB Ground Layout Around Connectors                                                     | 26 |

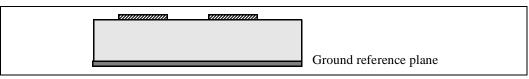

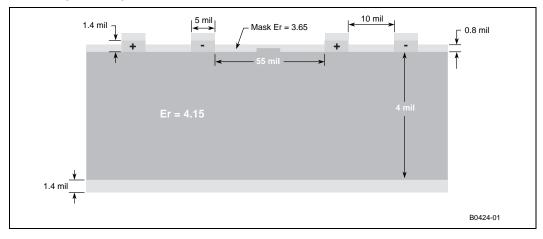

| 9  | Cross Section of Differential Trace                                                     |    |

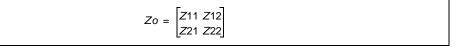

| 10 | LED and Serial EEPROM Configurations                                                    |    |

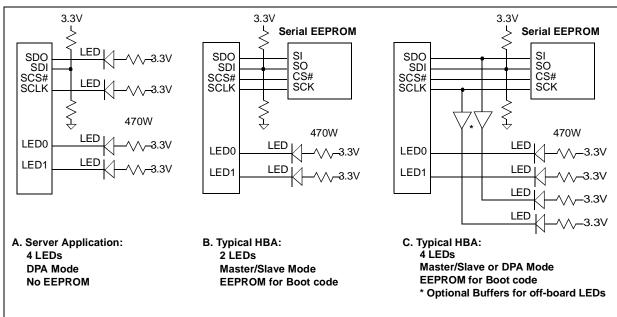

| 11 | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Connection Scheme - Normal Mode |    |

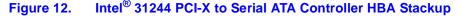

| 12 | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller HBA Stackup                     | 39 |

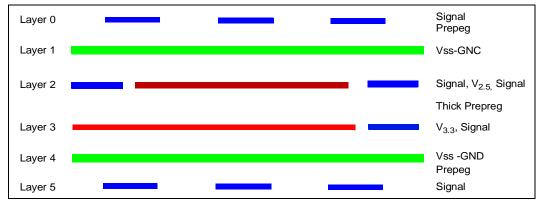

| 13 | Write Backplane Topology                                                                |    |

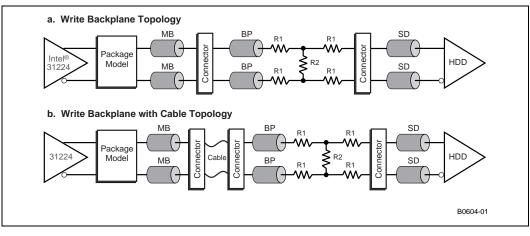

| 14 | Read Backplane Topology                                                                 | 41 |

| 15 | Microstrip Stackup                                                                      | 43 |

| 16 | Stripline Stackup                                                                       | 44 |

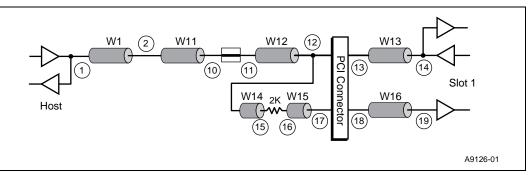

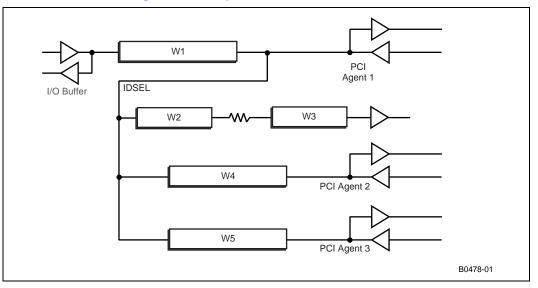

| 17 | Single-Slot Topology                                                                    | 52 |

| 18 | Embedded Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller                        |    |

|    | Design with Single PCI-X Load                                                           |    |

| 19 | Embedded PCI-X Design With Multiple Loads                                               |    |

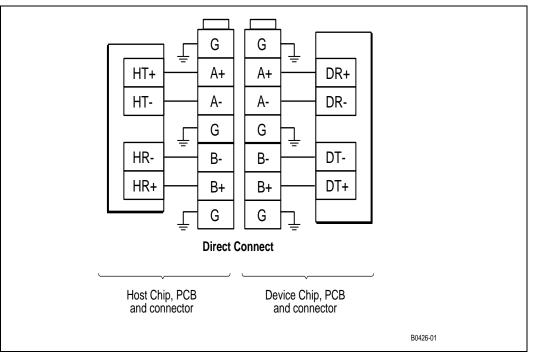

| 20 | Serial ATA Direct Connect                                                               |    |

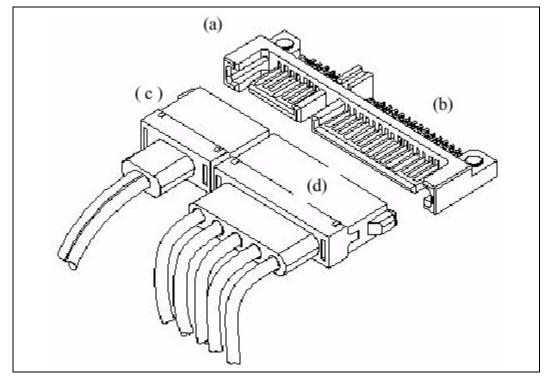

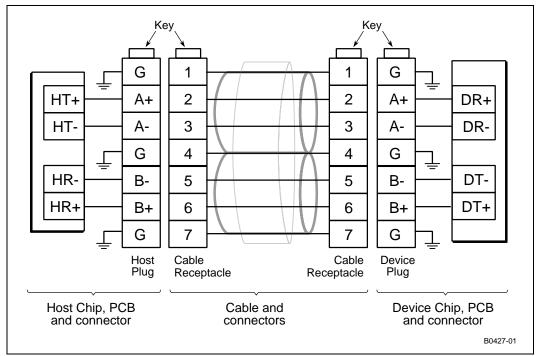

| 21 | Serial ATA Connectors Cable to Host Connections                                         |    |

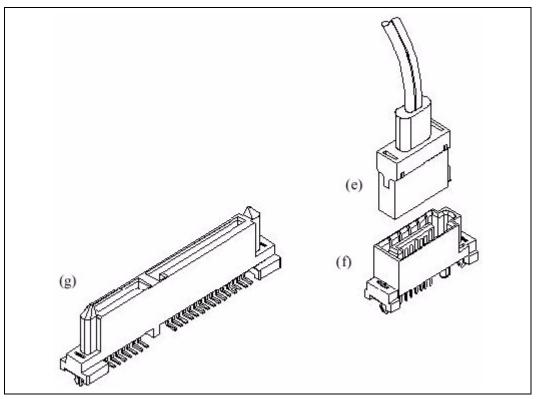

| 22 | Serial ATA Host Connectors                                                              |    |

| 23 | Serial ATA Cable Signal Connections                                                     |    |

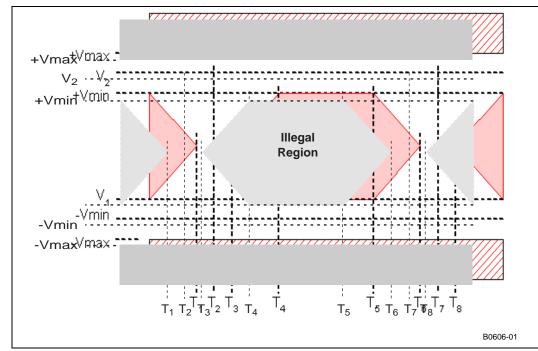

| 24 | Serial ATA Eye Diagram                                                                  |    |

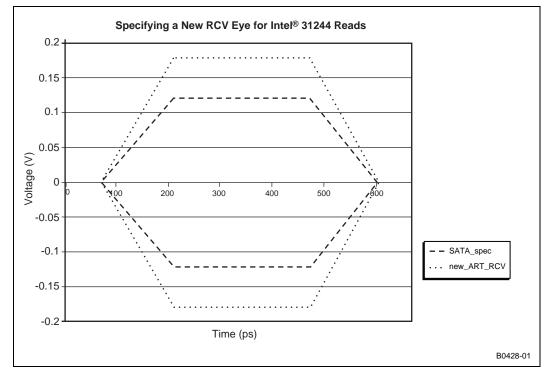

| 25 | Extended Mode Receiver Example                                                          |    |

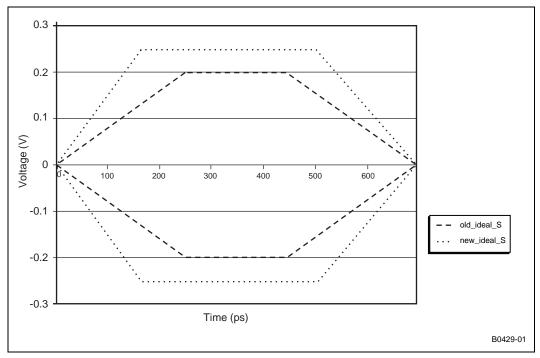

| 26 | Extended Mode Driver Example                                                            | 64 |

| 27 | Intel <sup>®</sup> IQ31244 PCI-X to Serial ATA Controller Evaluation Platform Board     |    |

|    | Block Diagram                                                                           | 67 |

# **Tables**

|                                                                                        | Reference Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 2                                                                                      | Terminology and Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| 3                                                                                      | Serial ATA Signals Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 18                                                                                                  |

| 4                                                                                      | PCI-X Bus Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| 5                                                                                      | Configuration Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |

| 6                                                                                      | JTAG Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

| 7                                                                                      | Serial ROM Interface Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

| 8                                                                                      | Power Supply Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

| 9                                                                                      | Normal Voltage Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

| 10                                                                                     | Extended Voltage Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

| 11                                                                                     | Normal Voltage Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

| 12                                                                                     | Motherboard Stackup, Microstrip                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |

| 13                                                                                     | Motherboard Microstrip Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                       |

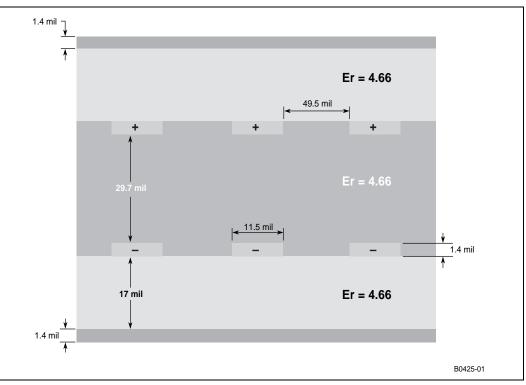

| 14                                                                                     | Backplane Stripline Stackup                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                       |

| 16                                                                                     | Backplane Stackup, Offset Stripline                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

| 15                                                                                     | Backplane Stackup, Microstrip                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

| 17                                                                                     | Cable Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

| 18                                                                                     | PCI/X Voltage Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

| 19                                                                                     | PCI-X Clocking Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

| 20                                                                                     | Add-on Card Routing Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |

| 21                                                                                     | PCI-X Slot Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

| 22                                                                                     | Wiring Lengths for Single Slot                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 52                                                                                                  |

| 23                                                                                     | Wiring Lengths for Embedded Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |

|                                                                                        | with Single PCI-X Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .53                                                                                                   |

|                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |

| 24                                                                                     | Wire Lengths For Multiple PCI-X Load Embedded                                                                                                                                                                                                                                                                                                                                                                                                                                                            | - 4                                                                                                   |

|                                                                                        | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |

| 25                                                                                     | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions                                                                                                                                                                                                                                                                                                                                                                                                          | .55                                                                                                   |

| 25<br>26                                                                               | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements                                                                                                                                                                                                                                                                                                                                                                  | . 55<br>. 61                                                                                          |

| 25<br>26<br>27                                                                         | Intel <sup>®</sup> 31Ž44 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement                                                                                                                                                                                                                                                                                                                                            | . 55<br>. 61<br>. 62                                                                                  |

| 25<br>26<br>27<br>28                                                                   | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver                                                                                                                                                                                                                                                                                                          | . 55<br>. 61<br>. 62<br>. 63                                                                          |

| 25<br>26<br>27<br>28<br>29                                                             | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver<br>Extended Mode Driver                                                                                                                                                                                                                                                                                  | . 55<br>. 61<br>. 62<br>. 63<br>. 64                                                                  |

| 25<br>26<br>27<br>28<br>29<br>30                                                       | Intel <sup>®</sup> 31Ž44 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver<br>Extended Mode Driver<br>Terminations: Pull-up/Pull-down                                                                                                                                                                                                                                               | . 55<br>. 61<br>. 62<br>. 63<br>. 64<br>. 65                                                          |

| 25<br>26<br>27<br>28<br>29<br>30<br>31                                                 | Intel <sup>®</sup> 31Ž44 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver<br>Extended Mode Driver<br>Terminations: Pull-up/Pull-down<br>Logic Analyzer Pod 1                                                                                                                                                                                                                       | .55<br>.61<br>.62<br>.63<br>.64<br>.65<br>.69                                                         |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32                                           | Intel <sup>®</sup> 31Ž44 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver<br>Extended Mode Driver<br>Terminations: Pull-up/Pull-down<br>Logic Analyzer Pod 1<br>Logic Analyzer Pod 2                                                                                                                                                                                               | .55<br>.61<br>.62<br>.63<br>.63<br>.64<br>.65<br>.69<br>.70                                           |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33                                     | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver<br>Extended Mode Driver<br>Terminations: Pull-up/Pull-down<br>Logic Analyzer Pod 1<br>Logic Analyzer Pod 2<br>Logic Analyzer Pod 3                                                                                                                                                                       | .55<br>.61<br>.62<br>.63<br>.64<br>.65<br>.69<br>.70<br>.71                                           |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>35                               | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver<br>Extended Mode Driver<br>Terminations: Pull-up/Pull-down<br>Logic Analyzer Pod 1<br>Logic Analyzer Pod 2<br>Logic Analyzer Pod 3<br>Logic Analyzer Pod 5                                                                                                                                               | .55<br>.61<br>.62<br>.63<br>.63<br>.64<br>.65<br>.69<br>.70<br>.71                                    |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>35<br>34                         | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions.<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver<br>Extended Mode Driver<br>Terminations: Pull-up/Pull-down<br>Logic Analyzer Pod 1<br>Logic Analyzer Pod 2<br>Logic Analyzer Pod 3<br>Logic Analyzer Pod 5<br>Logic Analyzer Pod 4                                                                                                                      | .55<br>.61<br>.62<br>.63<br>.64<br>.65<br>.69<br>.70<br>.71<br>.72<br>.72                             |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>35<br>34<br>36                   | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver<br>Extended Mode Driver<br>Terminations: Pull-up/Pull-down<br>Logic Analyzer Pod 1<br>Logic Analyzer Pod 2<br>Logic Analyzer Pod 3<br>Logic Analyzer Pod 5<br>Logic Analyzer Pod 4<br>Logic Analyzer Pod 6                                                                                               | .55<br>.61<br>.62<br>.63<br>.64<br>.65<br>.69<br>.70<br>.71<br>.72<br>.72<br>.72                      |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>35<br>34<br>36<br>37             | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver<br>Extended Mode Driver<br>Terminations: Pull-up/Pull-down<br>Logic Analyzer Pod 1<br>Logic Analyzer Pod 2<br>Logic Analyzer Pod 3<br>Logic Analyzer Pod 5<br>Logic Analyzer Pod 4<br>Logic Analyzer Pod 6<br>Thermal Resistance                                                                         | .55<br>.61<br>.62<br>.63<br>.64<br>.65<br>.69<br>.70<br>.71<br>.72<br>.72<br>.73<br>.77               |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>35<br>34<br>36<br>37<br>38       | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver<br>Extended Mode Driver<br>Terminations: Pull-up/Pull-down<br>Logic Analyzer Pod 1<br>Logic Analyzer Pod 2<br>Logic Analyzer Pod 3<br>Logic Analyzer Pod 5<br>Logic Analyzer Pod 4<br>Logic Analyzer Pod 6<br>Thermal Resistance<br>544-Lead H-PBGA Package Thermal Characteristics                      | .55<br>.61<br>.62<br>.63<br>.64<br>.65<br>.70<br>.71<br>.72<br>.72<br>.73<br>.77                      |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>35<br>34<br>36<br>37<br>38<br>39 | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver<br>Extended Mode Driver<br>Terminations: Pull-up/Pull-down<br>Logic Analyzer Pod 1<br>Logic Analyzer Pod 2<br>Logic Analyzer Pod 3<br>Logic Analyzer Pod 5<br>Logic Analyzer Pod 4<br>Logic Analyzer Pod 6<br>Thermal Resistance<br>544-Lead H-PBGA Package Thermal Characteristics<br>Design References | .55<br>.61<br>.62<br>.63<br>.64<br>.65<br>.69<br>.70<br>.71<br>.72<br>.72<br>.77<br>.77               |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>35<br>34<br>36<br>37<br>38       | Intel <sup>®</sup> 31244 PCI-X to Serial ATA Controller Design<br>Serial ATA Signal Definitions<br>Interface Timing and SI Requirements<br>Timing Requirement<br>Extended Voltage Mode Receiver<br>Extended Mode Driver<br>Terminations: Pull-up/Pull-down<br>Logic Analyzer Pod 1<br>Logic Analyzer Pod 2<br>Logic Analyzer Pod 3<br>Logic Analyzer Pod 5<br>Logic Analyzer Pod 4<br>Logic Analyzer Pod 6<br>Thermal Resistance<br>544-Lead H-PBGA Package Thermal Characteristics                      | .55<br>.61<br>.62<br>.63<br>.64<br>.65<br>.69<br>.70<br>.71<br>.72<br>.73<br>.77<br>.77<br>.79<br>.79 |

# **Revision History**

| Date                                      | Revision # | Description                                                                                                                                                                                |  |

|-------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| April 2004 003 Removed Section 5.4.5, "Sp |            | Removed Section 5.4.5, "Spread Spectrum Clocking" on page 35.                                                                                                                              |  |

|                                           |            | Removed SSC pin in Table 2, "Terminology and Definition" on page 9.                                                                                                                        |  |

|                                           |            | Updated SSCEN pin in Table 5, "Configuration Pin Descriptions" on page 20 and Table 30, "Terminations: Pull-up/Pull-down" on page 65.                                                      |  |

|                                           |            | Removed Section 9.1, "Power Delivery for the Intel® 31244 PCI-X to Serial ATA Controller (TBD)" on page 59.                                                                                |  |

|                                           |            | In Appendix A, "Intel <sup>®</sup> IQ31244 Controller Evaluation Platform Board Bill of Materials", replaced Bill of Materials table with a URL to the Intel <sup>®</sup> website.         |  |

| December 2002                             | 002        | In Section 2.1, added a new table titled "Serial ROM Interface Pin Descriptions".                                                                                                          |  |

|                                           |            | In Section 2.1, added note to Table 2, "Serial ATA Signal Pin Descriptions", indicating that LED2 and LED3 as dual purpose pins.                                                           |  |

|                                           |            | Replaced Figure 5, "PBGA Mapped by Pin Function" with a revised illustration.                                                                                                              |  |

|                                           |            | Added content to Section 3.4.1.1, "Intel GD31244 PCI-X to Serial ATA Controller Decoupling", regarding the use of at least twelve 0.1 $\mu$ F capacitors to decouple the VCC 2.5 V signal. |  |

|                                           |            | Removed Section 3.4.1.2, "PCI-X Decoupling".                                                                                                                                               |  |

|                                           |            | In Table 30, "Terminations: Pullup/Pulldown", revised row with signal name of TRST# to include TDI#, TMS#, and TCK as 4.7K pull-ups.                                                       |  |

|                                           |            | In Appendix A, revised the Bill of Materials.                                                                                                                                              |  |

| October 2002                              | 001        | Initial release of this document.                                                                                                                                                          |  |

intel®

# This page intentionally left blank.

# **1.1 Reference Documentation**

For the latest revision and documentation number, contact your Intel representative.

#### Table 1.Reference Documents

| Document                                                                                                                            | Intel Document Number or Source                                              |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Intel <sup>®</sup> Artisea PCI-X to Serial ATA Controller Developer's Manual                                                        | 273603                                                                       |

| Intel <sup>®</sup> Artisea PCI-X to Serial ATA Controller Datasheet                                                                 | 273595                                                                       |

| Intel <sup>®</sup> Packaging Databook                                                                                               | 240800                                                                       |

| Printed Circuit Board (PCB)Test Methodology User's Guide,<br>Revision 1.6                                                           | 298179<br>http://developer.intel.com/design/chipsets/<br>appInots/298179.htm |

| <i>Terminating Differential Signals on PCB</i> s, by Steve Kaufer and Kelee Crisafulli. Printed Circuit Design Magazine, March 1999 | http://www.pcdmag.com                                                        |

# **1.2 Terminology and Definitions**

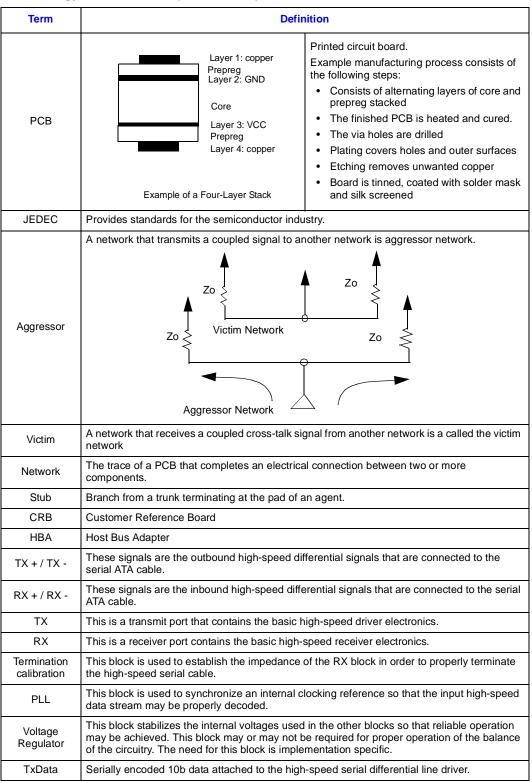

#### Table 2.Terminology and Definition (Sheet 1 of 3)

| Term                                                                                                                                                           | Definition                                                                                                                                                                  |                                                                                                                                                                                                                                                                                            |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Stripline                                                                                                                                                      |                                                                                                                                                                             | <ul> <li>Stripline in a PCB is composed of the conductor inserted in a dielectric with GND planes to the top and bottom.</li> <li>NOTE: An easy way to distinguish stripline from microstrip is that you need to strip away layers of the board to view the trace on stripline.</li> </ul> |  |

| Microstrip                                                                                                                                                     |                                                                                                                                                                             | Microstrip in a PCB is composed of the conductor on the top layer above the dielectric with a ground plane below                                                                                                                                                                           |  |

| Prepreg Material used for the lamination process of manufacturing epoxy material that is placed between two cores. This laye and forms around adjacent traces. |                                                                                                                                                                             |                                                                                                                                                                                                                                                                                            |  |

| Core                                                                                                                                                           | Material used for the lamination process of manufacturing PCBs. This material is two sided laminate with copper on each side. The core is an internal layer that is etched. |                                                                                                                                                                                                                                                                                            |  |

#### Table 2.Terminology and Definition (Sheet 2 of 3)

#### Table 2.Terminology and Definition (Sheet 3 of 3)

| Term                   | Definition                                                                                                                                                                                                                                                                                                                                 |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RxData                 | Serially encoded 10b data attached to the high-speed serial differential line receiver.                                                                                                                                                                                                                                                    |  |  |

| 10b encoding           | The 8B/10B encoding scheme transmits eight bits as a 10-bit code group. This encoding is used with Gigabit Ethernet, Fibre Channel and InfiniBand*.                                                                                                                                                                                        |  |  |

| Jitter                 | Jitter is a high-frequency, semi-random displacement of a signal from its ideal location.                                                                                                                                                                                                                                                  |  |  |

|                        | Inter-symbol interference. Data-dependent deterministic jitter caused by the time differences required for the signal to arrive at the receiver threshold when starting from different places in bit sequences (symbols).                                                                                                                  |  |  |

| ISI                    | For example media attenuates the peak amplitude of the bit sequence $[0,1,0,1]$ , more than it attenuates the peak amplitude of the bit sequence $[0,0,0,0,1,1,1,1]$ , thus the time required to reach the receiver threshold with the $[0,1,0,1]$ sequence is less than required from the $[0,0,0,0,1,1,1,1]$ sequence.                   |  |  |

| 151                    | The run length of 4 produces a higher amplitude which takes more time to overcome when changing bit values and therefore produces a time difference compared to the run length of 1-bit sequence. When different run lengths are mixed in the same transmission the different bit sequences (symbols) therefore interfere with each other. |  |  |

|                        | ISI is expected whenever any bit sequence has frequency components that are propagated at different rates by the transmission media. This translates into high-high-frequency, data-dependent, jitter.                                                                                                                                     |  |  |

| Differential<br>Signal | A signal derived by taking the difference between two conductors. In this spec a differential signal is comprised of a positive conductor and a negative conductor. The differential signal is the voltage on the positive conductor minus the voltage on the negative conductor (i.e., $TX+ - TX-$ ).                                     |  |  |

intel®

# This page left intentionally blank.

# int<sub>el</sub> overview

This document provides layout information and guidelines for designing platform or add-in board applications with the Intel® 31244 PCI-X to serial ATA controller (GD31244). It is recommended that this document be used as a guideline. Intel recommends employing best-known design practices with board-level simulation, signal integrity testing and validation for a robust design.

Designers should note that this guide focuses upon specific design considerations for the GD31244 and is not intended to be an all-inclusive list of all good design practices. It is recommended that this guide is used as a starting point and use empirical data to optimize your particular design.

This pre-silicon analysis information is preliminary and subject to change. Sections marked with Note: TBD are to be updated in future revisions.

#### 2.1 Features

The GD31244 is a state-of-the-art, PCI-X to Serial ATA Controller with four Serial ATA ports running at 1.5 Gbits/s. The device is targeted at embedded applications such as PC motherboards, as well as standalone PCI-X Host Bus Adapter (HBA) cards and RAID controllers.

The GD31244 is both a PCI-X Bus Master and Slave, which automatically switches modes as required.

As a PCI-X Slave, the device supports:

- I/O Reads

Configuration Read Configuration Write

- I/O Writes

- Memory Read Bus Cycles

As a PCI-X Bus Master, this device supports:

- Single Memory Reads · Line Memory Reads

- · Memory Writes Multiple Memory Reads

This device is compliant with a PCI-X bus operating at up to 64 bits at 133 MHz, resulting in burst data rates of 1064 Mbytes/s. The GD31244 provides four Serial ATA ports running at 1.5 Gbits/s transfer rate, which are compliant to the Serial ATA: High speed Serialized AT Attachment Specification, Revision 1.0e. The GD31244 derives its Serial ATA clocks from an internal PLL, with a reference clock of 37.5 MHz provided externally or from a crystal.

The GD31244 is fully compatible with parallel ATA operating system drivers and software. The chip may be configured in compatibility mode, mapping the PCI-X configuration space to match the x86 standard Primary and Secondary IDE ports. To support both on-board parallel IDE, plus the four Serial ATA ports, the chip may be configured for native PCI-X mode, allowing Plug-and-Play BIOS and operating systems to map the Serial ATA drives to non-conflicting task file and I/O address space. For higher performance in systems where compatibility is not required, all four channels may be configured as Direct Port Access (DPA).

Feature Highlights:

- Four SATA Channels at 1.5 Gbits/s

- Serial ATA: High speed Serialized AT Attachment Specification, Revision 1.0e Compliant

- 64-bit/133 MHz PCI-X Bus. Backwards compatible to 32-bit/33 MHz and 64-bit/66 MHz

- Compatible with existing Operating Systems

- Supports native PCI IDE

- Hot-Plug Drives

- Supports Master/Slave Mode for Compatibility with existing Operating Systems

- Supports SATA Direct Port Access (Master/Master Mode)

- Independent DMA Masters for each SATA Channel

- 3.3 V and 2.5 V Supply, 2 W maximum

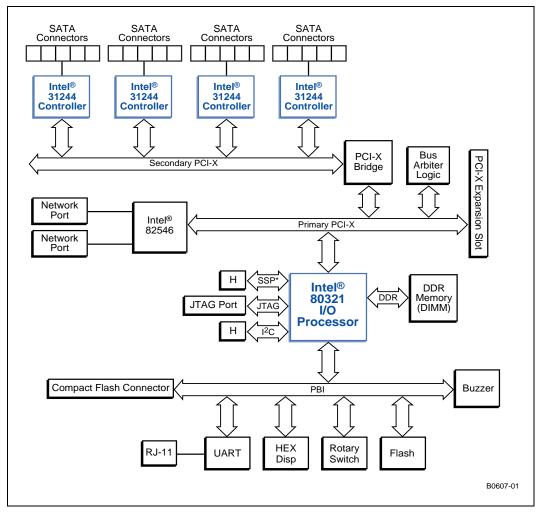

#### Figure 1. Intel<sup>®</sup> 31244 PCI-X to Serial ATA Controller Block Diagram

### 2.2 Applications

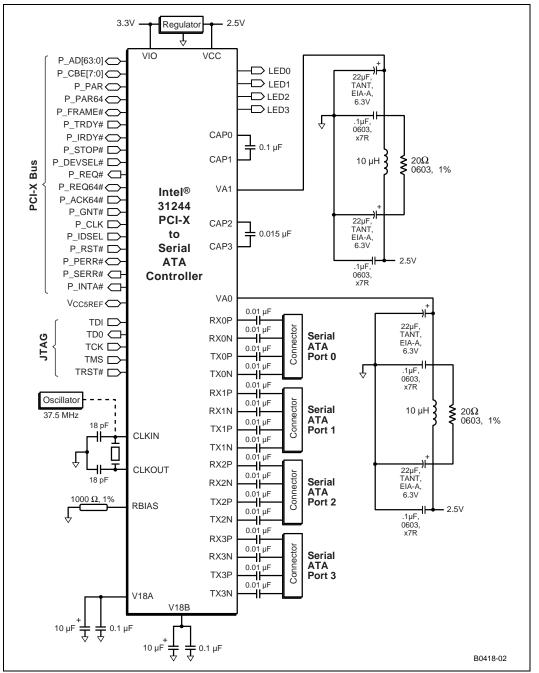

The GD31244 may be used to build a Serial ATA Host Bus Adapter which connects to the PCI-X bus. Control for external activity LEDs, a 37.5 MHz Crystal, a voltage regulator and some external resistors and capacitors are needed.

intel®

# This page left intentionally blank.

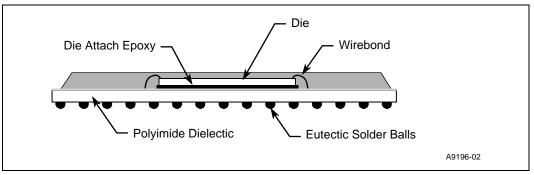

# Intel<sup>®</sup> 31244 PCI-X to Serial ATA Controller Package

The GD31244 signals, are located on a 256-pin Plastic Ball Grid Array (PBGA) package to simplify signal routing and system implementation. For detailed signal descriptions refer to the *Intel*<sup>®</sup> *31244 PCI-X to Serial ATA Controller Datasheet*. Contact your Intel sales representative to obtain a copy of this document. The construction of the packages is shown in Figure 3.

### 3.1 Signal Pin Descriptions

The signal pin descriptions for the GD31244 are provided as a reference. A complete list is also available in the *Intel*<sup>®</sup> 31244 PCI-X to Serial ATA Controller Datasheet.

#### Table 3.Serial ATA Signals Pin Descriptions

| Name                                                                                 | Description                                                                                                                                                                         |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX0P, TX0N,<br>TX1P, TX1N,<br>TX2P, TX2N,<br>TX3P, TX3N                              | <b>OUTPUT - Differential High-Speed Outputs:</b> These are the differential serial outputs for each channel. When disabled, these outputs are driven to their DC-Bias point.        |

| RX0P, RX0N,<br>RX1P, RX1N,<br>RX2P, RX2N,<br>RX3P, RX3N<br>RX3P, RX3N                |                                                                                                                                                                                     |

| CLKOUT <b>OUTPUT - LVTTL:</b> This is connected to one side of the 37.5 MHz crystal. |                                                                                                                                                                                     |

| CLKIN                                                                                | <b>INPUT - LVTTL:</b> This is the reference clock input for the clock multiplier unit at 37.5 MHz. It may be connected to either an external clock source or one side of a crystal. |

| CLKO                                                                                 | Buffered output of the 37.5 MHz clock.                                                                                                                                              |

| RBIAS                                                                                | <b>INPUT - ANALOG:</b> This pin is pull-down to ground with a 1000 $\Omega$ , 1% resistor in order to set the internal termination resistors to 1000 $\Omega$ .                     |

| CAP0, CAP1                                                                           | Analog: An external 0.1 $\mu F$ (+/- 10%) capacitor is connected between these pins to set the Clock Multiplier PLL loop filter response.                                           |

| LED0, LED1,<br>LED2 <sup>†</sup> , LED3 <sup>†</sup>                                 | <b>OUTPUT - LVTTL:</b> These are the Activity LED outputs for channel 0, channel1, channel 2 and channel 3 (active LOW with 10 mA maximum sink capability).                         |

† LED2 and LED3 are dual purpose pins. Refer to Table 7.

#### Table 4.PCI-X Bus Pin Descriptions (Sheet 1 of 2)

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CAP2, CAP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Analog: An external 0.015 $\mu F$ (+/- 10%) capacitor is connected between these pins to set the PCI PLL loop filter response.                                                                                                                                                                                                                                                                                                                              |  |

| P_ACK64# BIDIRECTIONAL - LVTTL: Indicates that the device has positively decoded its addu<br>the target of the current access and the target is willing to transfer data using the ful<br>data bus.                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| P_AD[63:0] BIDIRECTIONAL - LVTTL PCI Address and Data: The address and data lines are multiplexed on these pins. A bus transaction consists of an address phase followed b or more data phases. P_AD[63:56] contains the most significant byte and P_AD[7:0] or the least significant byte.                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| P_C/BE[7:0]#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>BIDIRECTIONAL - LVTTL:</b> Command and Byte Enable. The bus command and byte enable signals are multiplexed on these pins. During the address phase, the P_CBE# lines define the bus command. During the data phase, the P_CBE# lines are used as Byte Enables. The Byte Enables are valid for the entire data phase and determine which byte lanes carry meaningful data.                                                                               |  |

| P_CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | All PCI bus signals are referenced to this clock.                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| P_DEVSEL#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>BIDIRECTIONAL - LVTTL with Pull-Up Resistor:</b> Device Select. This signal is asserted by the target once it has detected its address. As a bus master, the P_DEVSEL# is an input signal to the Intel <sup>®</sup> 31244 PCI-X to serial ATA controller indicating whether any device on the bus has been selected. As a bus slave, the GD31244 asserts P_DEVSEL# to indicate that it has decoded its address as the target of the current transaction. |  |

| P_FRAME# BIDIRECTIONAL - LVTTL with Pull-Up Resistor: Cycle Frame. This signal is driven current master to indicate the beginning and duration of a transaction. P_FRAME# is asserted to indicate the start of a transaction and de-asserted during the final data ph                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| P_GNT# <b>INPUT - LVTTL. Grant:</b> This signal is asserted by the bus arbiter and indicates to the GD31244 that access to the bus has been granted. This is a point-to-point signal and master has its own GNT#.                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| P_IDSEL INPUT - LVTTL. Initialization Device Select: This signal is used as a chip select of PCI-X configuration read and write transactions. This signal is provided by the host systems.                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |